在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4 平台

2011-10-21 16:13:51 1270

1270

针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

2013-11-28 18:49:00 12149

12149

器件中选型。Xllinx公司的主流器件有Spartan-3E、Spartan-3A、Virtex-4LX、Virtex-4 SX、Virtex-4 FX、Virtex-5 LX、Virtex

2020-11-19 15:39:56 4945

4945

数字信号的输入和输出。对于在FPGA器件内实现的任何时序逻辑应用,失去了时钟信号便意味着信号的传输将处于停滞状态。时钟信号的重要性可见一斑。(特权同学,版权所有)图3.6 理想时钟波形FPGA器件

2019-04-12 01:15:50

FPGA实现高速FFT处理器的设计介绍了采用Xilinx公司的Virtex - II系列FPGA设计高速FFT处理器的实现方法及技巧。充分利用Virtex - II芯片的硬件资源,减少复杂逻辑,采用

2012-08-12 11:49:01

, Inc.) 日前宣布隆重推出EasyPath-6FPGA,该产品为高性能 FPGA 进入量产器件提供了六周内即可实现的总成本最低、风险最小的的解决方案,在所有FPGA降低成本解决方案中转入量产时间

2012-08-11 18:17:16

VIRTEX-4 - Tri-Mode Embedded Ethernet MAC Wrapper v4.4 - Xilinx, Inc

2022-11-04 17:22:44

VIRTEX-5FPGA - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

亲爱的社区成员,我正在实施XAPP861中推荐的8x过采样和数据恢复单元(DRU),以便在Virtex-4 FPGA上进行异步串行数据恢复。我通过3米DVI电缆接收了160bbps的8b10b编码流

2020-06-18 16:00:28

我们正在使用Virtex-4 ML423平台。是否有可能驾驶LVDS接头接口(文档UG087.pdf中没有12),电压不同于2.5伏?在ISE中,我在所需的端口上设置LVCMOS12,但我在LVDS

2019-08-14 08:45:01

嗨,我对Virtex-4中BRAM的工作频率有疑问。如果有人知道BRAM的最大工作频率是多少?提前致谢以上来自于谷歌翻译以下为原文hi, I have a question about

2018-10-10 11:53:12

嗨,我使用Virtex6 LX75T和4个高速DAC设计了一块威廉希尔官方网站

板。我将每个DAC连接到一个FPGA io Bank,我使用MRCC引脚作为MMCM(差分)的时钟输入,4个引脚用于片外反馈。不幸

2020-06-16 10:06:19

嗨,我需要Virtex-4器件“xc4vfx12”的门数值。如果有任何公式,我们可以用它来计算设备的可用门数。 CLBS,切片和其他资源,请告诉我。感谢致敬,的Sandip

2020-06-18 07:02:27

大家好,我正在研究包括3个不同时钟域的设计。我已经阅读了这个帖子,我发现与virtex-II和virtex-4相比,virtex-5在MTBF中是最差的。对于较低和实用的MTBF,我没有在同步器链

2020-06-12 09:27:03

嗨,XilinxIDF站点表明IDF仅支持Virtex-4,Virtex-5,Spartan-6和7系列FPGA。我可以在Xilinx Virtex-6 FPGA上使用IDF吗?有没有人尝试过使用IDF和Virtex-6 FPGA?谢谢,季米特里斯

2020-07-08 15:56:53

亲爱的先生,我们已经在我们的定制设计板上组装了Virtex-4 FPGA BGA封装,组装后我们进行物理检查时检查所有电源接地之间是否短路。请告诉我们调试此问题的任何过程并删除简短。 FPGA的稳压器威廉希尔官方网站

与FPGA IC隔离问候萨蒂亚

2020-06-19 07:42:07

的bitgen以及SEM IP内核可以做到这一点,但据我所知它们不能与virtex-4一起使用。有没有其他方法来估计virtex-4器件(XQR4VSX55)的基本位,以及我们如何计算同一器件的软

2019-02-26 10:24:45

连接的设备及其相应的设备ID。 现在,为了配置FPGA器件,我找到了Virtex-4系列的步骤,但它们恰好与Spartan 3E的步骤略有不同。那么,任何人都可以让我知道Spartan 3E系列FPGA

2019-06-12 09:45:38

Xilinx Virtex-II Pro 和 Virtex-II Pro X 器件能提供集成 PowerPC 内置技术的 FPGA,也是第一个能提供支持从 622 Mbps 到 10.3125

2013-09-06 16:28:27

本帖最后由 mr.pengyongche 于 2013-4-30 02:56 编辑

Xilinx Virtex-4 ML403嵌入开发平台原理图[url=www.0404.cc]

2012-08-17 09:12:44

描述 PMP9408 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨。它利用一个 PMBus 接口来实现电流

2022-09-21 07:56:06

描述PMP9408 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨。它利用一个 PMBus 接口来实现电流

2018-08-29 08:42:24

Virtex-4 XC4VFX12)。之后,我想将它移植到新平台(即Virtex-5 XC5VFX70T),但我的ISE Foundation 10.1安装不支持这个FPGA。我错过了什么吗? ISE

2018-11-15 11:30:24

你好,什么是运行EDK,Xilinx编程ML410或Virtex-4的最佳或至少可接受的要求?至于CPU速度,内存和磁盘容量?我现有的系统运行EDK样品需要45分钟以上!问候,Ramsin

2020-06-02 15:10:59

713.17 IOB寄存器和锁存器723.18 实现操作符及产生模块773.18.1 DSP48中运算符实现和模型生成(Virtex-4和Virtex-5器件)773.18.2 在乘法器中操作符实现

2012-04-24 09:18:46

是对时钟相位的控制精度相对较差。 在通讯领域里,用光纤传输高速数据是一个比较常用的解决方案。A1tera公司的StatixⅡGX和StatixⅢGX系列[1],Xllinx公司的Virtex-4

2012-02-22 13:58:51

为什么推出Virtex-5LXT FPGA平台和IP解决方案?如何打造一个适用于星形系统和网状系统的串行背板结构接口FPGA?

2021-04-29 06:18:31

提供 Virtex-4、Virtex-5、Virtex-6 、Virtex-7、 Kintex-7ZYNQ-7000系列等.. ALTERA优势产品系列:Stratix、 Arria、 Cyclone、 MAX、 Agilex系列等二手FPGA 货真价实

2019-07-28 17:47:39

嗨, 我正在开发一种设计,我们的主板有1个virtex5 fpga和9个从属卡,每个都有1个V5 fpga。我想同步所有9个从卡的操作。我还希望主卡和从卡之间的数据传输速率为300-400Mbps

2019-01-30 06:52:36

元件的输出是输入时钟延迟所得。延迟时间取决于延迟元件在延迟链路中的位置。这种延迟体现为针对原始时钟的相位改变或相移,这就是所谓的“数字相移”。图1所示的即为Virtex-4器件中的典型DCM模块。根据

2020-04-25 07:00:00

当我使用Actel FPGA中实现的简单擦洗保护Virtex4SX55时遇到问题。如果我选择“-g ReadBack”和“-g persist”选项,则Virtex4SX55中的程序将被Actel

2020-06-19 10:36:59

嗨,我想知道Virtex-6 FPGA可以预期多少时钟抖动。我已经阅读了有关Virtex-6 FPGA的所有文档,但没有找到数值。我发现的唯一的事情是它具有低抖动但不低或数值。

2020-06-12 14:56:20

的IDDR方法在Virtex-4和Virtex-5 FPGA中,赛灵思将其ILOGIC模块直接放置在I/O驱动器和接收器的后面。该模块包括4个存储元件寄存器和1个可编程绝对延迟元件。Virtex-4

2010-12-29 15:17:55

你好, 我做了一个关于回读virtex-4 FPGA的项目。 我想只使用没有.msk文件的CRC-32进行CRC校验,当然,我只回读MGT,CLB,IOB,DSP,CLK。无论FPGA工作与否,我认为这些都不可变。这是正确的?并告诉怎么做? 非常感谢!

2020-06-08 08:48:59

Clock Manager,数字时钟管理器)和Mulplier(乘法器)。其中CLB是FPGA具有可编程能力的主要承担者,Virtex-5的一个 slice的主要组成单元包括4个6输入查找表、4个

2018-10-18 16:29:45

知道我在Virtex-4上执行此操作时,为什么它会引用Virtex II?我是否需要指定不同于文件中的XmYn位置或其他XmYn位置而不是尝试指定SLICE?我不清楚X和Y是否直接对应于R和C,或者网格

2020-05-27 07:57:19

在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

Virtex-5 器件的输入端实现边沿对齐。要实现直接时钟控制读数据采集方法,这一点非常关键。所有合理的板设计工具都可以在可接受的容错范围内轻松满足这些布线长度。时序分析本 Virtex-5 QDR II

2019-04-22 07:00:07

嗨,我正在尝试从FPGA向另一个设备输出一个时钟信号(10MHz)来驱动一个50欧姆的端接负载。我试着用DDR来输出这个时钟。我从主振荡器时钟输入(50MHz)到virtex板生成此信号。我使用DCM以5来获得10Mhz。然后我把它运行到DDR。到目前为止,我没有运气。有人可以给我指点吗?谢谢。

2020-06-15 08:40:22

我们如何使用Virtex-4 FPGA的Block-RAM来存储矩阵/ Vector的内容。例如,如何在BRAM中存储矢量A = [1 2 4 5 6 7 9 3]?OR矩阵B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-27 06:43:47

我们如何使用Virtex-4 FPGA的Block-RAM来存储矩阵/ Vector的内容。例如,如何在BRAM中存储矢量A = [1 2 4 5 6 7 9 3]?OR矩阵B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-29 09:16:36

我们如何使用Virtex-4 FPGA的Block-RAM来存储矩阵/ Vector的内容。例如,如何在BRAM中存储矢量A = [1 2 4 5 6 7 9 3]?OR矩阵B = [1 2 3 45 6 7 8 9 1 4 5 232 1]

2020-05-29 14:41:56

我是VHDL和FPGA的新手。我有Virtex-4板,125 MHz时钟。我需要为模数转换(ADC)模块生成31.25 MHz(分频125 MHz×4)的串行时钟(SCLK)。任何人都可以帮助

2020-05-25 08:53:55

我有一台Memec Virtex-4 FX12 LC开发板,并希望使用u***对威廉希尔官方网站

板进行编程。是否可以使用Platform Cable USB II编程器对威廉希尔官方网站

板进行编程?谢谢,雨果

2019-09-27 07:28:35

使用STARTUP_VIRTEX4原语来控制CCLK和DONE信号。在生成比特流时,我使用了“-g DONE_cycle:KEEP”选项。根据我对闪存和Virtex-4之间接口的测量,这部分设计工作正常。我完全

2020-05-29 10:14:55

你好,我正在尝试做一个简单的显示应用程序来测试Virtex-4 VSK上的LCD。此应用程序在16x2 LCD上显示单行文本。除了micrlaze,bram / bram ctrls,lmb

2020-06-02 06:59:50

嗨,大家好!我正在使用带有Virtex-4的Nallatech Xtreme DSP套件,我需要使用DIME clock_A为ADC和DCA供电,以实现ADC / DAC的全时钟控制。但是没有准备

2019-09-19 10:58:49

存储器接口生成器(MIG)解决方案---Virtex-4 存储器接口和Virtex-II Pro存储器解决方案 Virtex-4? FPGAs solve

2009-10-24 12:02:14

#438。我发现Xilinx回答记录23873,这似乎是一个类似于我所看到的问题。我对提议的解决方案有些警惕,它使用4个BUFGMUX作为2:1时钟多路复用器,然后是基于常规逻辑的最终4:1输出多路复用

2018-09-29 14:50:00

嗨,我即将使用Virtex-4QV设备(XQR4VFX140)开始一个新项目。虽然我对使用DDR2 / DDR3 SDRAM的Xilinx MIG有一些经验,但我发现MIG IP不支持VIRTEX-4QV器件。那可能是另类?如何将DDR2 SDRAM与此FPGA连接?弥敦道

2020-04-02 06:08:46

近年来,随着FPGA技术的发展,支持重构的FPGA器件新品迭现。Xilinx、Altera、Lattice的FPGA器件都是SRAM查找表结构。Xilinx支持模块化动态部分重构的器件族有

2011-05-27 10:23:28

时钟线的简单方法来为FPGA外部的时钟供电。使用Virtex-6,我听说有一个新的“高性能”时钟(HPC),具有低抖动,用于将时钟直接从MMCM转发到IO。在计时资源用户指南(第34页)中,有人说

2020-06-10 16:36:37

标志着进入第三周期。等效时间采样技术的原理作用及采用FPGA器件实现系统的设计图4 波形仿真在第一个周期中从CLK 的第一个上升沿开始计时同时对CLK 进行分频可以得到CLK_ADC_OUT 时钟信号

2020-10-21 16:43:20

大家好我想使用Xilinx的Virtex-4芯片学习VHDL FPGA编程,以便:1.真正学习贸易(我是初学者,想在真实芯片上进行FPGA编程)。2.开发我自己的片上系统,这将成为实验设备的一部分

2018-09-28 16:54:33

你好。我是韩国LCD& Video Enginner使用各种Xilinx FPGA。我想看看Virtex-4 Video Starter Kit CD。如何收到Virtex-4视频入门套件

2020-06-12 16:17:40

锁定信号的上升沿是否与virtex-4 FPGA中DCM生成时钟的上升沿对齐?

2020-07-13 09:50:56

/fpga_sys_planner.htmVirtex-5 FXT, Virtex-5 LX, Virtex-5 LXT, Virtex-5 SXT, Virtex-4 FX, Virtex-4 LX, Virtex-4 SX

2013-03-14 11:49:58

赛灵思多平台Virtex-4 FPGA的性能及应用

赛灵思(Xilinx)的Virtex-4现场可编程门阵列(FPGA)是首款基于ASMBL(Advanced Silicon Modular Block)架构的多平台FPGA系列。通过采用不同的平台(LX、FX

2009-06-26 08:11:39 41

41 一种FPGA时钟网络中锁相环的实现方案:摘 要:本文阐述了用于FPGA 的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探

2009-08-08 09:07:22 25

25 Xilinx公司的Virtex-5 FXT FPGA器件在业界率先集成了嵌入式PowerPC 440处理器模块、高速RocketIO GTX收发器和专用XtremeDSP 处理能力。作为65nm Virtex-5系列的第四款平台,Virtex-5 FXT提供了极高的

2009-11-24 11:17:22 32

32 FPGA, PowerPC, Virtex-4, 开发平台,嵌入式系统,通信,数字视频, 微处理器摘要:Xilinx公司的Virtex-4 ML403嵌入开发平台是入门级的开发环境,它采用Xilinx的器件XC4VFX12-FF668-10C,支持多个时钟源

2009-11-24 11:33:00 85

85 Virtex-4 FPGA应用指南

使用Virtex-4器件的DDR2控制器(267MHz及以上)

DDR2SDRAM器件提供了比DDRSDRAM指标所要求的更好的新功能,并允许DDR2器件以666Mb/s的数据

2010-05-13 14:14:26 39

39 Virtex-4 系列应用指南

利用直接时钟控制技术实现存储器接口数据采集

本应用指南介绍了在 VirtexTM-4 器件中实现存储器接口的直接时钟控制数据采集

2010-05-13 14:16:59 22

22 重点设计并实现了863项目“南海深水区动力环境立体检测技术研发”中5频段微波辐射计的数据处理与控制系统,以Xilinx公司Virtex-4系列FPGA为核心,包括数据采集、AGC自动增益控制、

2010-07-28 16:12:45 29

29 本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 Virtex-6 FPGA ML605开发评估技术方案

Virtex-6 FPGA是Xilinx公司的目标设计平台,提供集成的软件和硬件,有利于设计集中力量进性产品创新. Virtex-6系列包括LXT, SXT和HXT子系列,适

2010-04-22 18:07:58 3615

3615

Virtex-7 2000T FPGA的容量是市场同类最大28nm器件的2倍,而且比赛灵思最大型Virtex-6 FPGA大2.5倍。虽然2000T由4个切片组成,但它仍然保持着传统FPGA的使用模式,设计人员可通过赛灵思工具流程

2011-10-26 09:11:30 2795

2795 Xilinx Virtex-4 LX160/200 开发工具套件提供了让设计师加速产品上市的完整硬件环境。本套件针对 Xilinx 创新的 Virtex-4 Platform FPGA 系列,为设计的开发和测试提供了稳定的平台。

2012-01-17 14:08:38 2293

2293

Xilinx 的 Virtex-4 系列将高级硅片组合模块 (ASMBL) 架构与种类繁多的灵活功能相结合,大大提高了可编程逻辑设计能力,从而成为替代 ASIC 技术的强有力产品。Virtex-4 FPGA 由 LX、FX 和 SX 三

2012-01-17 16:14:24 6

6 The PPC405 Virtex-4 is a wrapper around the Virtex-4PowerPC 405 Processor Block primitive.

2012-02-10 16:57:58 38

38 PLL),再到Virtex-6基于PLL的新型混合模式时钟管理器MMCM(Mixed-Mode Clock Manager),实现了最低的抖动和抖动滤波,为高性能的FPGA设计提供更高性能的时钟管理功能。

2017-02-11 09:14:01 1030

1030

本文主要介绍利用FPGA的自身的特性实现随机数发生器,在Virtex-II Pro开发板上用ChipScope观察随机数序列,以及在PCIe4Base(基于Virtex-4 FPGA)上实现。

2017-02-11 16:26:11 12113

12113

介绍一种采用FPGA(现场可编程门阵列威廉希尔官方网站

)实现SDH(同步数字体系)设备时钟芯片设计技术,硬件主要由1 个FPGA 和1 个高精度温补时钟组成.通过该技术,可以在FPGA 中实现需要专用芯片才能实现的时钟芯片各种功能,而且输入时钟数量对比专用芯片更加灵活,实现该功能的成本降低三分之一.

2017-11-21 09:59:00 1840

1840

赛灵思Virtex® UltraScale ™ All Programmable FPGA 是高端FPGA 系列的扩展,可支持1Tbps 系统的实现。Virtex UltraScale 系列具有

2017-11-18 04:15:03 1797

1797

树结构 针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

2017-11-22 07:09:36 8891

8891

在本视频中,了解Xilinx采用高带宽存储器(HBM)和CCIX技术的16nm Virtex UltraScale + FPGA的功能和存储器带宽。

2018-11-27 06:20:00 3624

3624 Virtex®-6 FPGA内置支持PCIExpress®Gen2兼容接口。

本视频介绍了在ML605评估套件上运行的用于PCI Express技术的Virtex-6 FPGA集成模块的三个演示。

2018-11-22 06:30:00 2820

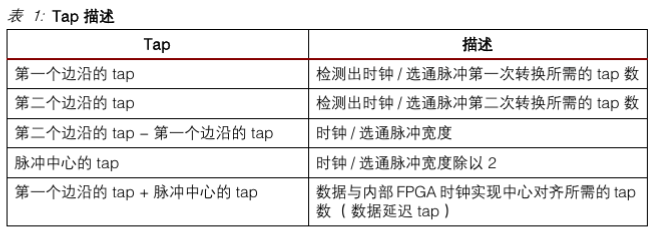

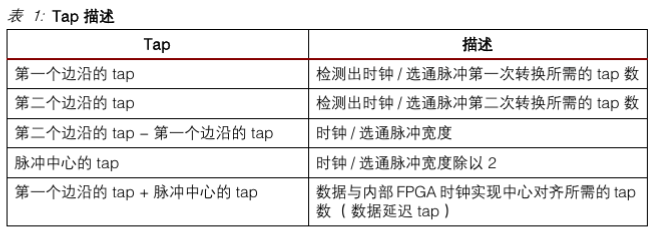

2820 大多数存储器接口都是源同步接口,从外部存储器器件传出的数据和时钟/ 选通脉冲是边沿对齐的。在 Virtex-4 器件采集这一数据,需要延迟时钟/ 选通脉冲或数据。利用直接时钟控制技术,数据经延迟

2020-04-11 09:55:08 743

743

xilinx公司推出的两种新Virtex-4 FPGA器件LX60和SX35.LX60是逻辑最佳LX平台的第二个器件,SX35是DSP最佳SX平台的第一个器件.和今年六月份提供的Virtex-4 LX25一起,Xilinx公司现在可提供三种革命性的FPGA系列.

2020-09-10 08:47:00 1846

1846 Virtex-4、Virtex-5和Spartan-3系列器件增加和修改了一些与配置有关的专用引脚,这些专用引脚如下。

2021-01-06 17:13:52 14

14 本节介绍0.80 mm和1.00 mm间距倒装芯片细间距BGA封装中Virtex-4设备的引脚。Virtex-4设备仅在高性能倒装芯片BGA封装中提供,这些封装经过优化设计,可改善信号完整性和抖动

2021-01-25 08:00:00 4

4 本应用指南描述了在 Virtex™-4 XC4VLX25 FF668 -10C 器件中实现的 DDR SDRAM 控制器。该实现运用了直接时钟控制技术来实现数据采集,并采用自动校准威廉希尔官方网站

来调整数据线上的延迟。

2021-03-26 14:42:41 4

4 对于一个设计项目来说,全局时钟(或同步时钟)是最简单和最可预测的时钟。只要可能就应尽量在设计项目中采用全局时钟。FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。

2021-04-24 09:39:07 5827

5827

介绍了eMMC 芯片的技术特点、工作原理,以及控制器的设计方案。该设计基于Xilinx公司的Virtex-6系列FPGA芯片,实现了控制器的设计方案,并给出了仿真结果,验证了该设计方案的可行性。此外,该设计均采用硬件逻辑实现,具有速度快、通用性强、可靠性高的特点。

2021-10-15 18:00:24 5

5

电子发烧友App

电子发烧友App

评论