资料下载

×

基于FPGA的AVS帧内预测的研究与设计单天燕

消耗积分:1 |

格式:pdf |

大小:822KB |

2017-03-08

基于FPGA的AVS帧内预测的研究与设计_单天燕

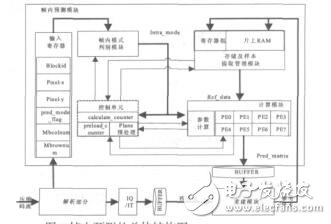

AVS 标准是我国具备自主知识产权的数字音视频编码标准, 可以广泛应用到高清、IPTV、数字电视等相关音视频领域。与当前国际上最先进的视频编码标准 H.264 相比,AVS 专利费、计算复杂度、存储器需求和存储带宽都有所降低 。AVS 标准主要是针对高清大尺寸数字视频制定的, 而高清序列的解码速度是衡量解码器性能的关键因素。为了提高解码速度,本文采用并行工作方式的 FPGA 硬件威廉希尔官方网站 实现。并行工作方式的 FPGA 具有延时短、集成度高、可靠性高等优点。另外 FPGA 设计方式灵活,可裁减、可扩充、可升级,给 AVS 视频解码器提供了一种有效的解决方案。帧内预测是视频编解码的重要部分, 其主要作用是降低视频图像的空间冗余。为了提高硬件资源的可重用性,节约硬件资源,设计了通用运算单元和模式转换子模块;另外在控制单元采用有效的控制逻辑,设计了预处理模块,提高了预测速度,最后在结合 AVS 参考模型 RM52j 和 verilog 语言的 DPI 接口建立的验证平台上,验证了该模块功能的正确性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章