Xilinx FPGA的GTx的参考时钟

可编程逻辑

描述

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

参考时钟的模式

参考时钟可以配置为输入模式也可以是输出模式,但是在运行期间不能切换。作为输入时,用于驱动Quad 或者channel PLLs,作为输出时,可以来自于同一个Quad中的任意一个channel。7系列的GTx只能作为输入,而Ultra和Ultra+系列的还可以作为输出。

作为输入模式时,7系列和Ultra是通过50Ω连接到4/5MGTAVCC上,Ultra+是通过50Ω连接到MGTAVCC上。后端根据不同系列器件给到不同IBUFDS_GTE。

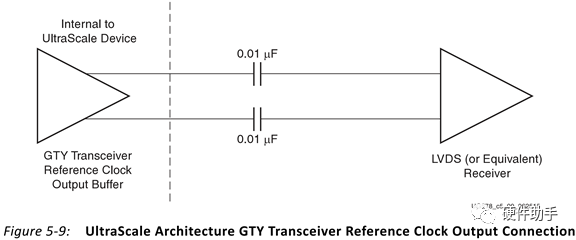

作为输出模式时,可以配置为从OBUFDS_GTE3/4或者OBUFDS_GTE3/4_ADV输出,UseOBUFDS_GTE3/4 when the RXRECCLKOUT is always derived from the same channel.如果提供RXRECCLKOUT的通道在运行时可以改变,则使用OBUFDS_GTE3/4_ADV。

参考时钟的选择

7系列FPGA中的GTP收发器提供不同的参考时钟输入选项。时钟选择和可用性与7系列GTX/GTH收发器略有不同之处在于,参考时钟路由是东西向而不是南北向。只能复用邻近的四分器的相同半部分(一个四分器分为两半部分)(参考时钟提供给PLL在一个给定的四也可以从相邻的四在同一个设备的一半来源。位于设备上半部分的Quad可以与位于上半部分的其他Quad共享其两个本地参考时钟。类似地,位于设备下半部的Quad可以与位于下半部的另一个Quad共享其两个参考时钟。)

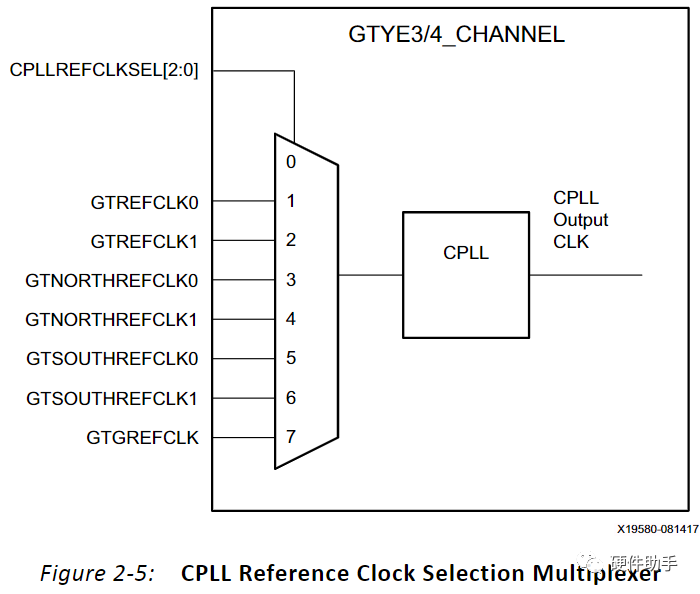

7系列FPGA中的GTX/GTH收发器提供不同的参考时钟输入选项。时钟选择和可用性类似于Virtex-6 FPGA GTX/GTH收发器,但参考时钟选择架构同时支持基于LC槽(或QPLL)和环形振荡器(或CPLL)的PLL。可以复用邻近上下两个Quad (一个 Quad 的参考时钟( Q ( n ))也可以通过 GTNORTHREFCLK 从下面的 QUAD (n-1))获得,或者从上面的 QuAD ( Q + 1 )获得。第三次。用于支持堆叠硅互连的器件(SSI)技术,经由GTNORTHREFCLK和GT SOUT REF CLK端口的参考时钟共享被限制在其自己的超级逻辑区域(SLR)内。)

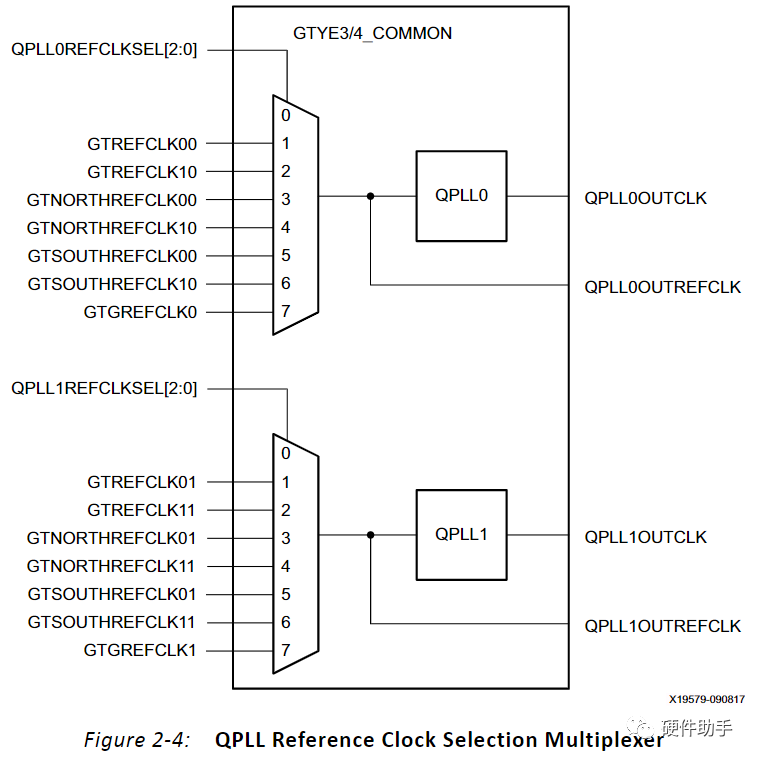

UltraScale设备中的GTH收发器提供不同的参考时钟输入选项。时钟选择和可用性类似于7系列FPGA GTX/GTH收发器,但参考时钟选择架构支持两个LC槽(或QPLL)和一个基于环形振荡器(或CPLL)的PLL。可以复用邻近的上下各两个Quad(Quad的参考时钟(Q(n)))也可以从下面最多两个Quad中获得(q(n-1)或q(n-2))通过GTSOUTHREFCLK通过GTNORTHREFCLK或从最多两个四次(Q(n+1)或Q(n+2))通过GTSOUTHREFCLK。

对于支持堆叠硅互连(SSI)技术的器件,通过GT NORT HRE FCLK和GTSOUTREFCLK端口共享的参考时钟被限制在其自己的超级逻辑区域(SLR)内。)

UltraScale设备中的GTY收发器提供不同的参考时钟输入选项。时钟选择和可用性是类似于7系列fpga gtx/gth收发器,但参考时钟选择架构支持两个液晶池(或qp ll)和一个环形振荡器(或cpll)基于锁相环,可以复用邻近的上下各两个四路。

对应的时钟源有如下区分:

GTP对应的每个GTP E2_公共在一个四通道有四个时钟输入可用:

两个本地参考锁引脚对,GTREFCLK0或GTREFCLK1

来自位于设备同一部分的另一个四角点的两个参考时钟针对

7系列的GTX/GTH对应的每个GTX/GTH收发器通道在四通道有六个时钟输入可用:

两个本地参考锁引脚对,GTREFCLK0或GTREFCLK1

两个参考时钟引脚对从四方以上,GTSOUTHREFCLK0或GTSOUTHREFCLK1

两个来自以下四角点的参考时钟针对,GTNORTHREFCLK 0或GTNORTHREFCLK 1

过度的和超+系列的GTx对应的四哈希时钟输入中的收发器信道:

两个本地参考锁引脚对,GTREFCLK0或GTREFCLK1

来自上述四角点的两个参考时钟针对,GTSOUTHREFCLK 0或GTSOUTHREFCLK 1

两个来自以下四角点的参考时钟针对,GTNORTHREFCLK 0或GTNORTHREFCLK 1

针对Ultra和Ultra+系列的参考时钟源不是10个的原因详见UG576和UG578。

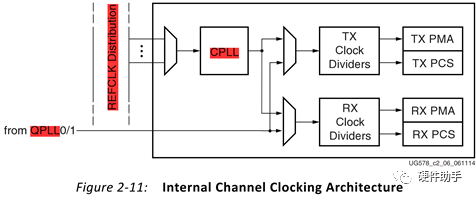

QPLL/CPLL

QPLL的质量比CPLL好,最好使用QPLL。

REFCLK

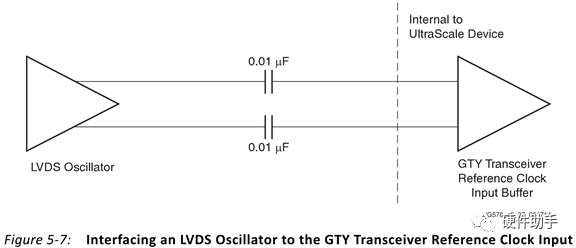

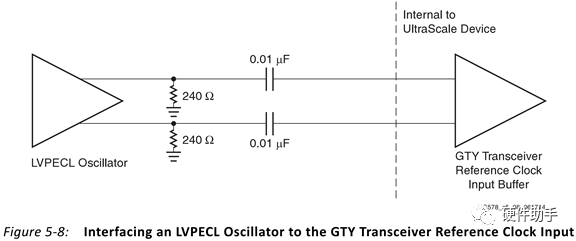

REFCLK的电平标准为LVDS或者LVPECL,都必须有AC耦合电容,电容的作用如下:

阻断振荡器和GTY收发器四专用时钟输入引脚之间的直流电流(这也降低了两个部分的功耗)。

共模电压无关。

交流耦合电容器与片上终端形成高通滤波器,衰减参考时钟的漂移。

当输入电平为LVPECL时,需进行直流偏置,偏置电阻的值优先满足晶振的要求。

当输入电平为LVDS时,The nominal range is 250 mV–2000 mV and the nominal value is 1200mV.

当使用多个时钟引脚时,可以使用外部缓冲器从同一个振荡器中驱动它们。当同一个quad使用了不用的时钟输入引脚时,可以使用外部时钟buffer提供外同步时钟!

审核编辑:汤梓红

-

用于FPGA的xilinx gtx phy是否支持SSC时钟?2019-04-01 0

-

如何使用相邻GTX磁贴的外部时钟2020-06-18 0

-

深度解析Xilinx FPGA的GTx的参考时钟2020-11-14 15144

-

请问GTX TXCLKOUT没有问世?2020-07-19 0

-

介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题2021-11-11 0

-

XILINX FPGA和Altera的相关资料推荐2021-12-28 0

-

Virtex6 FPGA GTX和Spartan6 FPGA GTP收发器的电源模块2017-04-05 1292

-

Xilinx全局时钟的使用和DCM模块的使用2017-11-22 10289

-

基于Xilinx FPGA用于ASIC前端验证的问题总结2018-12-22 1771

-

Xilinx 7系列FPGA时钟和前几代有什么差异?2021-03-22 4941

-

GTX/GTH收发器时钟架构应用介绍2021-03-29 6763

-

Xilinx 7系列FPGA收发器架构之硬件设计指导(一)2021-11-06 899

-

Xilinx FPGA平台GTX简易使用教程(一)2022-03-01 4746

-

Xilinx FPGA时钟资源概述2023-07-24 908

-

Xilinx 7系列FPGA的时钟结构解析2023-08-31 2622

全部0条评论

快来发表一下你的评论吧 !