深度解析Xilinx FPGA的GTx的参考时钟

电子说

描述

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

参考时钟的模式

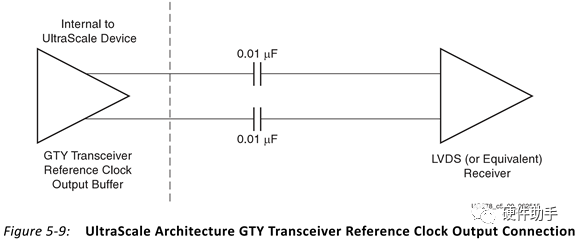

参考时钟可以配置为输入模式也可以是输出模式,但是在运行期间不能切换。作为输入时,用于驱动Quad 或者channel PLLs,作为输出时,可以来自于同一个Quad中的任意一个channel。7系列的GTx只能作为输入,而Ultra和Ultra+系列的还可以作为输出。

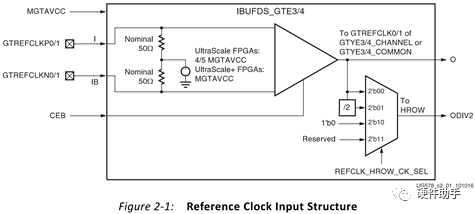

作为输入模式时,7系列和Ultra是通过50Ω连接到4/5MGTAVCC上,Ultra+是通过50Ω连接到MGTAVCC上。后端根据不同系列器件给到不同IBUFDS_GTE。

作为输出模式时,可以配置为从OBUFDS_GTE3/4或者OBUFDS_GTE3/4_ADV输出,UseOBUFDS_GTE3/4 when the RXRECCLKOUT is always derived from the same channel. UseOBUFDS_GTE3/4_ADV if the channel providing RXRECCLKOUT can change duringruntime.

参考时钟的选择

The GTP transceivers in 7 series FPGAs providedifferent reference clock input options. Clock selection and availabilitydiffers slightly from 7 series GTX/GTH transceivers in that reference clockrouting is east and west bound rather than north and south bound. 只能复用邻近的Quad的相同半部分(一个Quad分为两半部分)(the reference clock supplied to the PLLs in a given Quad can also besourced from the adjacent Quad in the same half of the device. A Quad locatedin the top half of the device can share its two local reference clocks with theother Quad located in the top half. Similarly, a Quad located in the bottomhalf of the device can share its two reference clocks with the other Quadlocated in the bottom half.)

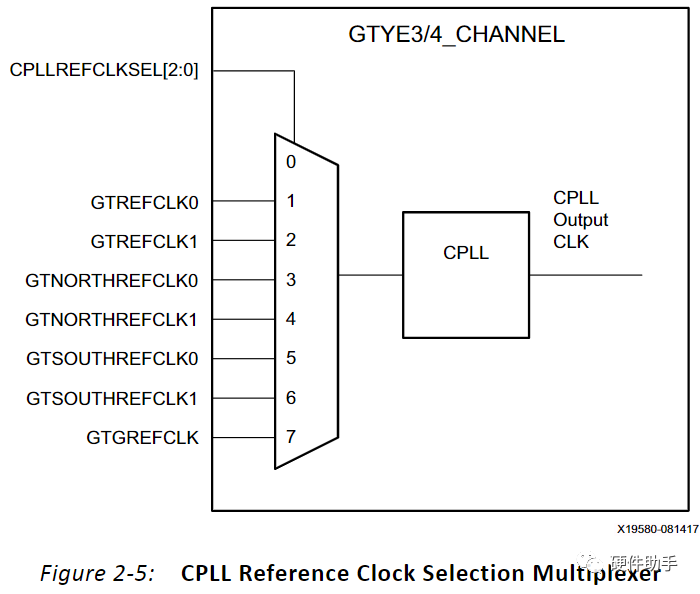

The GTX/GTH transceivers in 7 series FPGAs providedifferent reference clock input options. Clock selection and availability issimilar to the Virtex-6 FPGA GTX/GTH transceivers, but the reference clockselection architecture supports both the LC tank (or QPLL) and ring oscillator(or CPLL) based PLLs. 可以复用邻近上下两个Quad(the reference clock for a Quad (Q(n)) can also be sourced from theQuad below (Q(n–1)) via GTNORTHREFCLK or from the Quad above (Q(n+1)) viaGTSOUTHREFCLK. For devices that support stacked silicon interconnect (SSI)technology, the reference clock sharing via GTNORTHREFCLK and GTSOUTREFCLKports is limited within its own super logic region (SLR).)

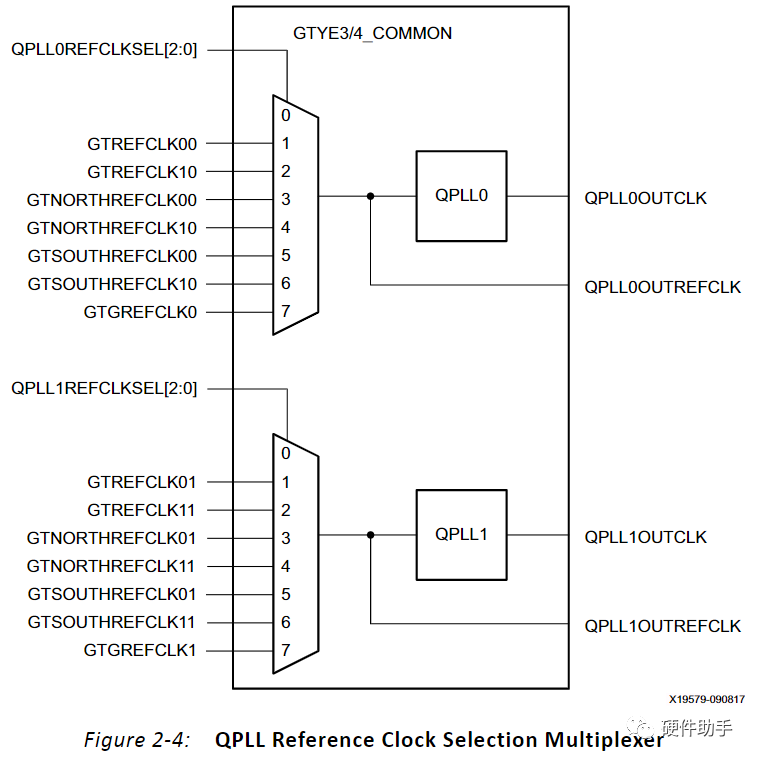

The GTH transceivers in UltraScale devices providedifferent reference clock input options. Clock selection and availability issimilar to the 7 series FPGAs GTX/GTH transceivers, but the reference clockselection architecture supports two LC tanks (or QPLL) and one ring oscillator(or CPLL) based PLLs. 可以复用邻近的上下各两个Quad(the reference clock for a Quad (Q(n)) can also be sourced from up totwo Quads below (Q(n–1) or Q(n-2)) via GTNORTHREFCLK or from up to two Quadsabove (Q(n+1) or Q(n+2)) via GTSOUTHREFCLK.

For devices that support stacked siliconinterconnect (SSI) technology, the reference clock sharing via GTNORTHREFCLKand GTSOUTREFCLK ports is limited within its own super logic region (SLR).)

he GTY transceivers in UltraScale devices providedifferent reference clock input options. Clock selection and availability issimilar to the 7 series FPGAs GTX/GTH transceivers, but the reference clockselection architecture supports two LC tanks (or QPLL) and one ring oscillator(or CPLL) based PLLs. 可以复用邻近的上下各两个Quad.

对应的时钟源有如下区分:

① GTP对应的Each GTPE2_COMMON in a Quad hasfour clock inputs available:

- Two local referenceclock pin pairs, GTREFCLK0 or GTREFCLK1

- Two reference clock pinpairs from the other Quad situated in the same half of the device

② 7系列的GTX/GTH对应的Each GTX/GTH transceiver channel ina Quad has six clock inputs available:

- Two local referenceclock pin pairs, GTREFCLK0 or GTREFCLK1

- Two reference clock pinpairs from the Quads above, GTSOUTHREFCLK0 or GTSOUTHREFCLK1

- Two reference clocks pinpairs from the Quads below, GTNORTHREFCLK0 or GTNORTHREFCLK1

③ Ultra和Ultra+系列的GTx对应的transceiver channel in a Quad hassix clock inputs available:

- Two local referenceclock pin pairs, GTREFCLK0 or GTREFCLK1

- Two reference clock pinpairs from the Quads above, GTSOUTHREFCLK0 or GTSOUTHREFCLK1

- Two reference clocks pinpairs from the Quads below, GTNORTHREFCLK0 or GTNORTHREFCLK1

④ 针对Ultra和Ultra+系列的参考时钟源不是10个的原因详见UG576和UG578。

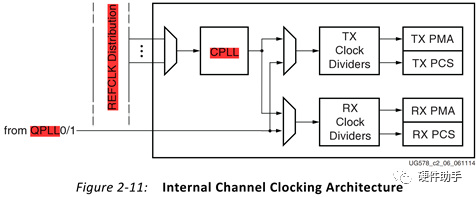

QPLL/CPLL

QPLL的质量比CPLL好,最好使用QPLL。

REFCLK

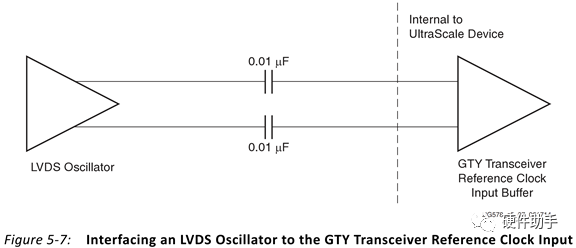

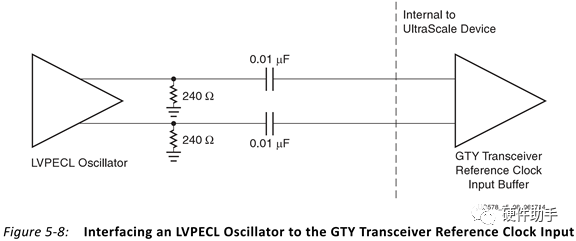

REFCLK的电平标准为LVDS或者LVPECL,都必须有AC耦合电容,电容的作用如下:

① Blocking a DC current betweenthe oscillator and the GTY transceiver Quad dedicated clock input pins (which reduces the power consumptionof both parts as well).

② Common mode voltage independence.

③ The AC coupling capacitor formsa high-pass filterwith the on-chip termination that attenuates a wander of the reference clock.

当输入电平为LVPECL时,需进行直流偏置,偏置电阻的值优先满足晶振的要求。

当输入电平为LVDS时,The nominal range is 250 mV–2000 mV and the nominal value is 1200mV.

When multiple clock pins are used, an external buffer can be used to drive them from the same oscillator. 当同一个quad使用了不用的时钟输入引脚时,可以使用外部时钟buffer提供外同步时钟!!!

编辑:hfy

-

用于FPGA的xilinx gtx phy是否支持SSC时钟?2019-04-01 0

-

如何使用相邻GTX磁贴的外部时钟2020-06-18 0

-

请问GTX TXCLKOUT没有问世?2020-07-19 0

-

介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题2021-11-11 0

-

XILINX FPGA和Altera的相关资料推荐2021-12-28 0

-

Virtex6 FPGA GTX和Spartan6 FPGA GTP收发器的电源模块2017-04-05 1292

-

Xilinx全局时钟的使用和DCM模块的使用2017-11-22 10296

-

基于Xilinx FPGA用于ASIC前端验证的问题总结2018-12-22 1771

-

Xilinx 7系列FPGA时钟和前几代有什么差异?2021-03-22 4947

-

GTX/GTH收发器时钟架构应用介绍2021-03-29 6772

-

Xilinx 7系列FPGA收发器架构之硬件设计指导(一)2021-11-06 901

-

Xilinx FPGA平台GTX简易使用教程(一)2022-03-01 4749

-

Xilinx FPGA时钟资源概述2023-07-24 909

-

Xilinx 7系列FPGA的时钟结构解析2023-08-31 2622

-

Xilinx FPGA的GTx的参考时钟2023-09-15 3690

全部0条评论

快来发表一下你的评论吧 !