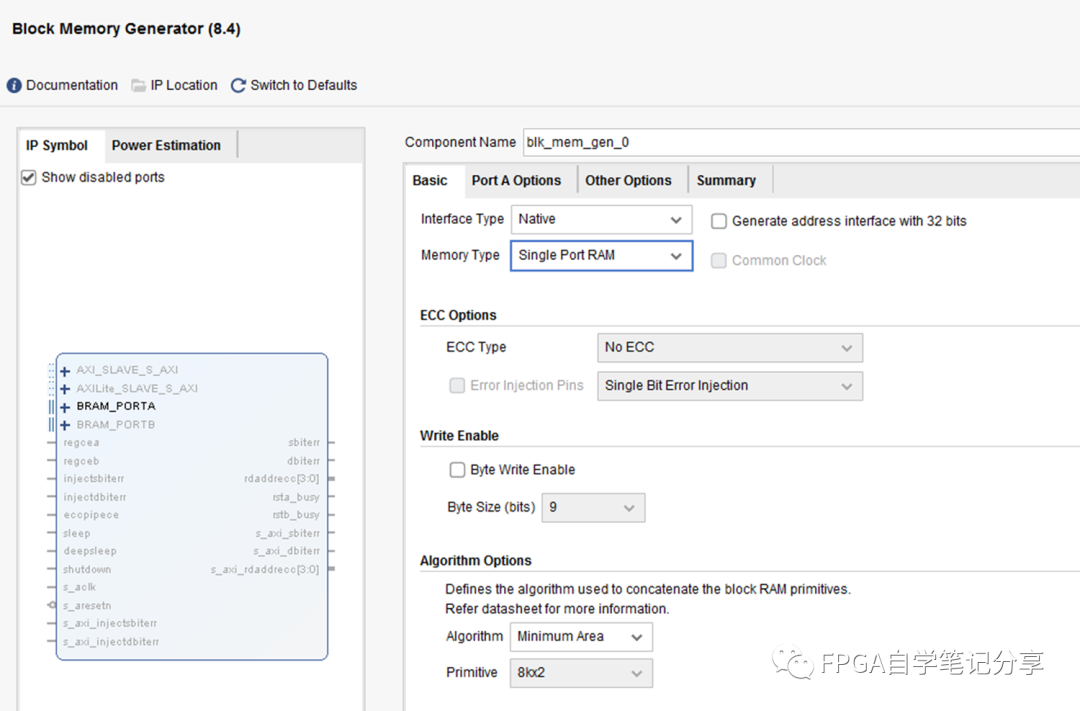

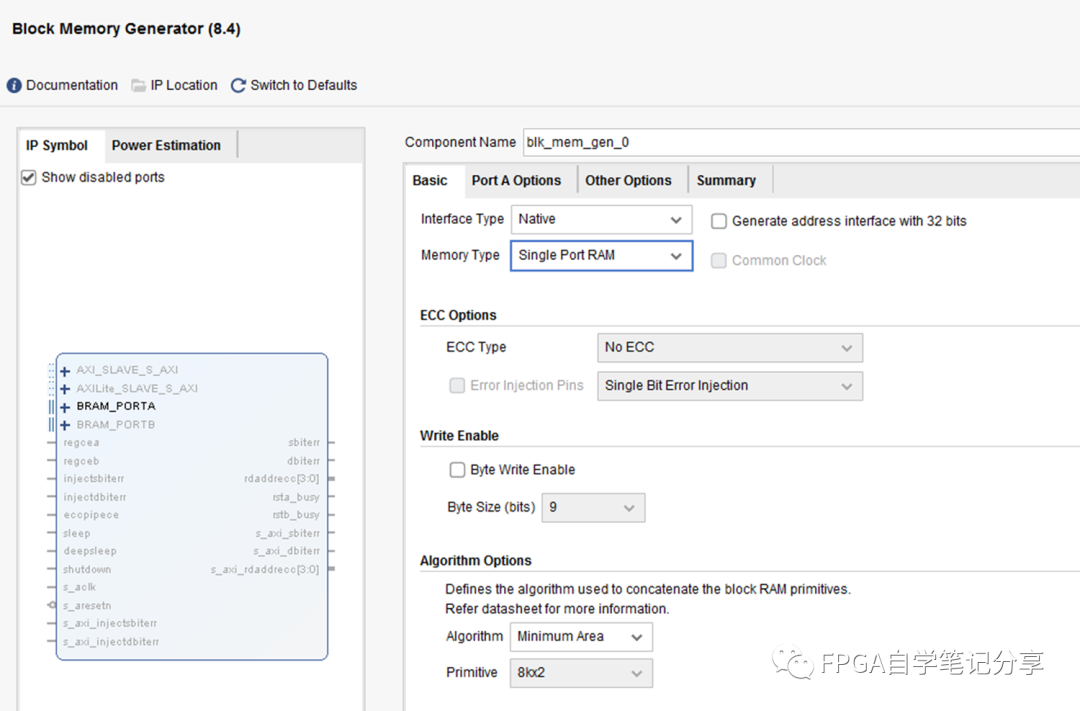

Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

2023-11-14 17:49:43 736

736

ISE 是 Xilinx 公司提供的集成化 FPGA 开发软件,它的主要功能包括设计输入(DesignEntry)、综合(Synthesis)、仿真(Simulation)、实现

2018-09-27 09:29:57

FPGA与CPLD的辨别和分类,总结的太棒了

2021-04-29 06:34:19

本帖最后由 eehome 于 2013-1-5 10:08 编辑

FPGA学习总结[经典推荐]

2012-05-14 16:59:49

你好: 我是一个购买的帐户,所以我的许可证应该允许访问所有内容。但是当我使用System Generator for DSP时,系统说我的SysGen签出许可证失败了。有人知道怎么解决吗?谢谢

2019-01-28 07:16:36

错误:System Generator for DSP(SysGen)的许可证签出失败。无法联系Xilinx许可证管理器。请检查以下内容:(1)XILINX环境变量指向有效的ISE安装(2

2018-12-29 10:35:12

FPGA中的数字控制器是什么?System Generator中的PID控制器是如何设计的?

2021-04-08 06:51:46

大家好,这是我第一次使用System Generator工具,如果有人能够解决一个不让我继续参与我的硬件协同仿真项目的问题,我想。我正在使用Matlab R2013b,Xilinx ISE 14.7

2020-03-23 06:53:11

根据我的理解,System Generator是MatLab到RTL的转换,因此不包括Vivado的优化过程。问题1--是真的。确实,Vivado中的优化将大大改变系统描述,而系统描述不会向后兼容

2019-04-25 12:47:45

HI,我正在使用System Generator 2014.4 30天评估包,Matalb 2014B。简单地说我想使用FIR编译器,当我尝试编辑它的参数时,我得到了两个错误: - 1.“来自MEX

2020-03-24 09:01:59

with FIR compiler 5.0 , in system generator. When i givea inputsinewave( amplitude of 1, 1 MHz

2019-02-12 11:20:48

/fpga-design/simulink-with-xilinx-system-generator-for-dsp.htmlhttp://www.mathworks.cn/searchresults/?c%5B%5D

2013-10-05 11:59:34

USE和System Generator何时才能胜任64位Windows 7?以上来自于谷歌翻译以下为原文When will ISE and System Generator be qualified for 64 bit Windows 7?

2018-11-26 15:05:56

最近在搞system generator仿真,发现getway in这个模块参数设置变化导致MATLAB闪退问题,贴图如下其中getway in 这个模块数据类型换成定点有符号或者无符号数都不得行,换成布尔值又会出现错误,不知为何啊!求教。

2018-01-05 21:43:53

翻译成verilog,在FPGA里面实现,即system generator。altera有没有类似的接口,与matlab可以互连,直接在matlab里设计我所需要的算法,在翻译成verilog?

2015-01-14 14:20:50

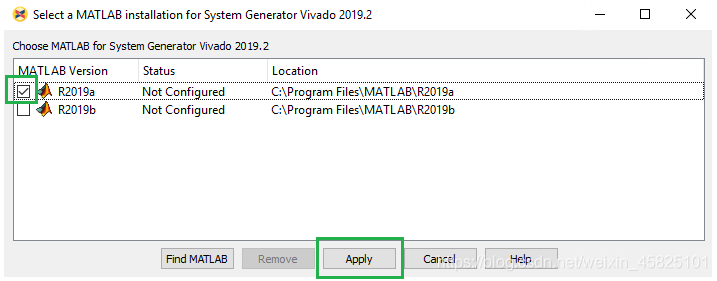

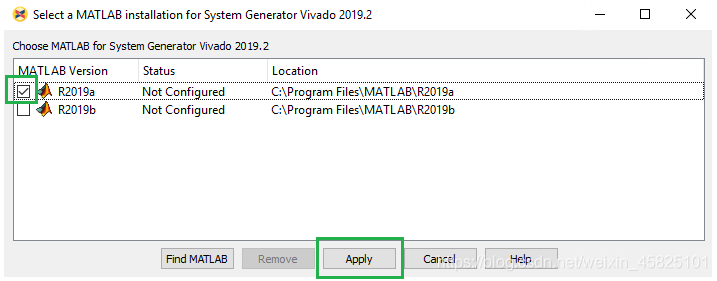

. But when it comes on selecting Matlab version for System generator 10.1 it displays both versions

2019-05-27 06:30:15

组的FPGA实现7.7 本章小结第8章基于System Generator的DSP系统开发技术8.1 System Generator的简介与安装8.1.1 System Generator简介

2012-04-24 09:23:33

,使用System Generator有三大优势:第一,图形化操作,简单易用;第二,实现的算法能确保与仿真结果相符;第三,无需为仿真和实现建立不同的模型。因此,利用 System Generator可以大幅度减少用FPGA设计DSP的工作量,缩短开发周期。

2019-06-21 06:25:23

各位好,最近在使用system generator 搭建一个ifft设计模块,使用ise调用,但是在下载到板子后,示波器输出波形去在没有输入的情况下仍然有波形,确定不是噪声,波形还是很规律,求解释呀!

2016-07-13 13:21:30

使用system generator导入xilinx模块时,只要连线两个模块,matlab就崩溃,有知道原因的大佬吗?

2018-01-19 17:54:57

几天前从学长那里装了candence软件16.5版本的软件,但是其中一个部分FPGA system planner 里的元器件不全,没有v7的FPGA,而且里面的操作界面也不一样,关键是我已经破解

2014-04-30 14:50:06

Suite下。在我的PC上,Xilinx System Generator嵌套在Vivado下。可以使用基于Vivado的System Generator来开发ISE系统吗?或者是否有必须安装

2018-12-27 10:55:34

哪位大佬能提供FSP(FPGA System Planer)的使用教程?跪求

2020-06-19 11:31:29

大家好,我正在使用具有Virtex-4 FX100的定制板。在内部,有一个基于VHDL的框架,它将定制板上的不同部分与“DSP内核”连接,后者是在System Generator下开发的。在这

2019-01-15 10:39:11

在system generator中,我把(-128~127),变为(-1~1),但是下载到硬件中,使用chipscope抓取到的数据确实(-128~127),请问是怎么回事

2016-08-10 15:32:38

有做System Generator处理图像的吗?遇到一些问题,一起商量下

2020-09-28 19:04:58

嗨,我正在尝试学习如何使用System Generator来创建自己的IP核。首先,我在DocNav中找到了一个ug948-vivado-sysgen-tutorial文档。我在哪里可以找到本文档中描述的示例?我在安装目录中的“examples”文件夹中找不到完全相同的示例。提前致谢马丁

2020-05-22 07:22:09

你好,我有兴趣使用Artix-7 FPGA进行以太网协同仿真(在Simulink中通过System Generator)。在System Generator中,我看到AC701

2020-07-15 08:45:40

本文以FPGA为核心构建了一种通用的雷达回波信号实时模拟系统。该系统采用FPGA作为回波信号模拟的运算单元,充分利用了FPGA资源丰富、并行处理能力强的特点,提高了系统的实时性;采用System

2021-04-29 06:14:20

各位大佬,我在安装System Generator时,跟着教程走,发现在vivado中没有出现System Generator for DSP这个选项,请问是我哪里安装得不对吗?

2023-09-26 21:54:58

当我完成SDx 2017.2的安装时,没有安装System Generator的选项。我正在运行从Xilinx下载的安装程序:https://www.xilinx.com/member/forms

2019-01-07 10:59:00

你好,我叫Joaquín。有人知道,我可以在Matlab / Simulink中使用System Generator创建一个双向(inout)端口。我正在尝试为Xilinx的外部存储器创建一个接口

2019-05-09 14:36:24

最近在使用system generator设计一个rs编码译码的模型,总的思想是在rs编码产生信号后,插入一个误码,然后作为信号源进行解码,看是否能够正常的进行解码,求解是怎么才能把rs编码后的信号存储起来作为信号源

2016-07-20 20:13:59

System Generator for DSP的特点是什么?如何使用System Generator for DSP实现系统级建模?怎么在Matlab中实现数字通信FPGA硬件设计?

2021-04-29 06:20:46

有用Xilinx的system generator做图像处理的嘛?求交流 。我正在用这个做图像处理,已经用了3个月了,在做一些算法,遇到一些困难,求一起交流学习。发现用这个开发的人真不多啊。

2014-05-09 14:57:21

入门设计实验.zip7.FPGA数字信号处理设计教程-system generator入门与提高.pdf`

2018-08-20 11:10:23

非常苦恼,刚开始学习system generator,用带光盘的书上的例子,想要学习一下设计流程,结果屡屡碰壁。在搭建好系统,点击开始仿真之后,总是会出错。在别人的电脑上就能仿真成功,一开始认为是

2016-07-13 23:12:36

xilinx公司的网络教程“利用 System Generator 进行 DSP 设计”谁有?上传一份给小弟吧

2013-03-14 12:17:03

以前,我们有Matlab 2006a和ISE 8.2i,并且正在使用System Generator。我们不得不重新安装Matlab 2006a以启用新的工具箱,但现在Simulink中没有

2018-11-19 14:42:56

亿海微6系 EQ6HL45型可编程逻辑芯片开发平台采用核心板加扩展板的模式,方便用户对核心板的二次开发利用,为前期验证和后期应用提供了可能。相信这样的一款产品非常适合从事FPGA开发的工程师、科研人员等群体。

2022-02-16 17:06:51

System Generator 是一种新型的基于FPGA 的信号处理建模和设计工具。本文首先介绍了System Generator 的主要特色和设计流程,然后基于此工具给出了Lorenz 混沌威廉希尔官方网站

设计的一种新方案并将

2009-07-08 15:02:28 24

24 System Generator for DSP 是一款具有高抽象层的设计工具,为算法开发人员和系统架构师从 Simulink 算法参考模型过渡到FPGA 硬件实施技术提供了一种高效的途径,且无需任何 HDL 编码工作

2010-06-10 08:21:19 29

29

采用Gardner算法,对QPSK调制解调系统中的位同步系统进行设计与实现,大大提高了系统性能和资源利用率。重点阐述采用FPGA开发环境System Generator系统设计工具进行位同

2010-07-21 16:12:40 26

26 Intel Agilex® F系列FPGA开发套件Intel Agilex® F系列FPGA开发套件设计用于使用兼容PCI-SIG的开发板开发和测试PCIe 4.0设计。该开发套件还可通过硬核处理器

2024-02-27 11:51:58

用matlab来实现fpga功能的设计

摘要:System Generator for DSP是Xilinx公司开发的基于Matlab的DSP开发工具?熗?时也是一个基于FPGA的信号处理建模和设计工具。

2008-01-16 18:10:54 11207

11207

深入了解赛灵思System Generator中的时间参数

基于模型的设计(MBD)因其在缩小实时系统抽象的数学建模和物理实现之间差距方面的光明前景而备受关注。通过使用相同的

2009-12-29 11:40:30 1300

1300

HDL设计和验证与System Generator相结合

Xilinx®SystemGeneratoRForDSP是用来协助系统设计的MATLABSimulink模块集。SystemGeneratorforDSP在熟悉的MATLAB环境中引入XilinxFPGA对象,让您能够

2010-01-06 14:39:30 1181

1181

System Generator 工具由 MathWorks 与 Xilinx 合作开发而成,DSP 设计人员可使用 MATLAB 和Simulink 工具在 FPGA 内进行开发和仿真来完善 DSP 设计。 该工具为系统级 DSP 设计与 FPGA 硬件实现的融合起

2011-05-11 18:36:23 224

224 该设计是基于System Generator设计平台,在Matlab/Simulink环境下搭建系统模型,再进行功能仿真和验证,完成QPSK调制器的设计。仿真结果表明,所设计的调制器能产生正确QPSK波形,达到了预期效果

2011-10-17 16:10:51 65

65 Xilinx公司推出的DSP设计开发工具System Generator是在Matlab环境中进行建模,是DSP高层系统设计与Xilinx FPGA之间实现的桥梁。在分析了FPGA传统级设计方法的基础上,提出了基于System Generator的

2013-01-10 16:51:24 58

58 完整性高的FPGA-PCB系统化协同设计工具 Cadence OrCAD and Allegro FPGA System Planner便可满足较复杂的设计及在设计初级产生最佳的I/O引脚规划,并可透过FSP做系统化的设计规划,同时整合logic、

2013-04-08 11:07:53 0

0 Xilinx FPGA工程例子源码:System Generator的设计实例

2016-06-07 14:41:57 22

22 单片机(Microcontrollers)学习,FPGA学习总结[经典推荐],感兴趣的小伙伴可以瞧一瞧。

2016-11-03 15:15:39 153

153 、乘加(MACC, ),乘加,三输入加法等等。该架构还支持串联多个DSP48E1 slice,避免使用fpga逻辑功能的繁琐。 System generator DSP48E1 模块参数 双击dsp48e1模块

2017-02-08 01:07:12 595

595

环境 Matlab 2014 a Vivado 2014.4 System generator 2014.4 实现步骤 1、模型搭建与仿真 在simulink环境下工程搭建如下 图3 四路加

2017-02-08 01:10:08 473

473

最新版System Generator支持快速开发和实现基于All Programmable FPGA、SoC和MPSoC的无线电设计 赛灵思日前宣布推出高级设计工具System Generator

2017-02-09 01:23:41 279

279 一直都在System Generator下做图像处理相关的算法,感觉SysGen挺强大的,前几天突发奇想,能否直接用SysGen实现数据的通信呢,毕竟一句HDL代码都不写对于做FPGA的人来说却是很有吸引力的。

2017-02-10 19:51:11 2618

2618

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可是设置

2017-02-11 11:53:11 3778

3778

system generator是xilinx公司的系统级建模工具,它是扩展mathworks公司的MATLAB下面的simulink平台,添加了XILINX FPGA专用的一些模块。加速简化了FPGA的DSP系统级硬件设计。

2017-02-11 19:21:33 7386

7386

利用System Generator软件平台,实现基于模块化建模方法的变换器建模,并简化语言编写控制系统的复杂过程。研究了从MATLAB-Xilinx环境中导出使用模块化建模方法搭建的控制算法。通过

2017-11-15 14:31:34 4985

4985

现在的FPGA算法的实现有下面几种方法: 1. Verilog/VHDL 语言的开发 ; 2. system Generator; 3. ImpulsC 编译器实现从 C代码到 HDL 语言; 4.

2017-11-17 14:29:06 7298

7298 Cadence OrCADFPGA System Planner为FPGA和PCB之间的协同设计提供了一种全面的、可扩展的解决方案,它能使用户创建一个正确的、最优的引脚分配。FPGA的引脚分配是根据

2017-11-17 20:36:09 5453

5453

在FPGA平台上应用System Generator工具实现了高精度频率估计Rife算法。不同于传统的基于HDL代码和IP核的设计方法,采用System Generator工具可以使复杂算法

2017-11-18 09:01:51 2208

2208

Xilinx System Generator 是专门为数字信号算法处理而推出的模型化设计平台,可以快速、简单地将DSP系统的抽象算法转换成可综合的、可靠的硬件系统,弥补了大部分对C语言以及Matlab工具很熟悉的DSP工程师对于硬件描述语言VHDL和Verilog HDL认识不足的缺陷。

2018-07-19 09:32:00 3716

3716

PLD/FPGA 常用开发软件System Generator 9.10。 业内领先的高级系统级FPGA开发高度并行系统。

2017-11-26 11:34:56 12

12 华为在FPGA领域深耕多年,有着全球最专业的FPGA开发团队,积累了大量FPGA开发经验和IP,这些积累结合其领先的弹性云服务架构,可以为用户提供简单易用的FPGA云服务。总结起来,华为FPGA云加速服务优势体现在以下技术方面。

2018-04-18 11:00:00 10023

10023

本视频产品演示介绍了 Xilinx 系统生成器(System Generator)和 Xilinx ISE® 项目浏览器(Project Navigator)设计环境之间的新整合。

2018-06-06 13:46:00 3024

3024

关键词: System Builder , SmartFusion FPGA 带有System Builder设计工具的Libero SoC软件可以加快SmartFusion2的开发和缩短客户的上市

2018-09-25 09:07:01 513

513 了解如何将Vivado HLS设计作为IP模块整合到System Generator for DSP中。

了解如何将Vivado HLS设计保存为IP模块,并了解如何将此IP轻松整合到System Generator for DSP的设计中。

2018-11-20 05:55:00 2940

2940 了解如何在System Generator中使用多个时钟域,从而可以实现复杂的DSP系统。

2018-11-27 06:42:00 3450

3450 了解如何使用Vivado System Generator for DSP进行点对点以太网硬件协同仿真。

System Generator提供硬件协同仿真,可以将FPGA中运行的设计直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

4262 System Generator 数字上下变频 (DUC/DDC)模块集的易用性大幅提升,使得更加便于无线算法开发。这些新型模块还添加了有助于加速验证和编译运行时间的增强功能,所有这些模块提供了七八种参数设置。

2019-07-31 09:22:49 2293

2293 近年来,在数字通信、网络、视频和图像处理领域,FPGA已经成为高性能数字信号处理系统的关键元件.FPGA的逻辑结构不仅包括查找表、寄存器、多路复用器、存储器,而且还有快速加法器、乘法器和I/O处理

2020-09-24 20:11:32 1336

1336

本文档的主要内容详细介绍的是Xilinx 7 系列FPGA中的Serdes总结。

2020-12-31 17:30:58 25

25 根据椭圆曲线密码体制的几种关键算法,采用Modelsim仿真工具设计相应的算法模块。然后将各模块代码通过System Gene

2021-06-12 10:17:00 1294

1294

STM8和STM32开发总结

2021-11-23 18:07:06 23

23 本篇博文是面向希望学习 Xilinx System Generator for DSP 入门知识的新手的系列博文第一讲。其中提供了有关执行下列操作的分步操作方法指南。

2022-02-16 16:21:36 1578

1578

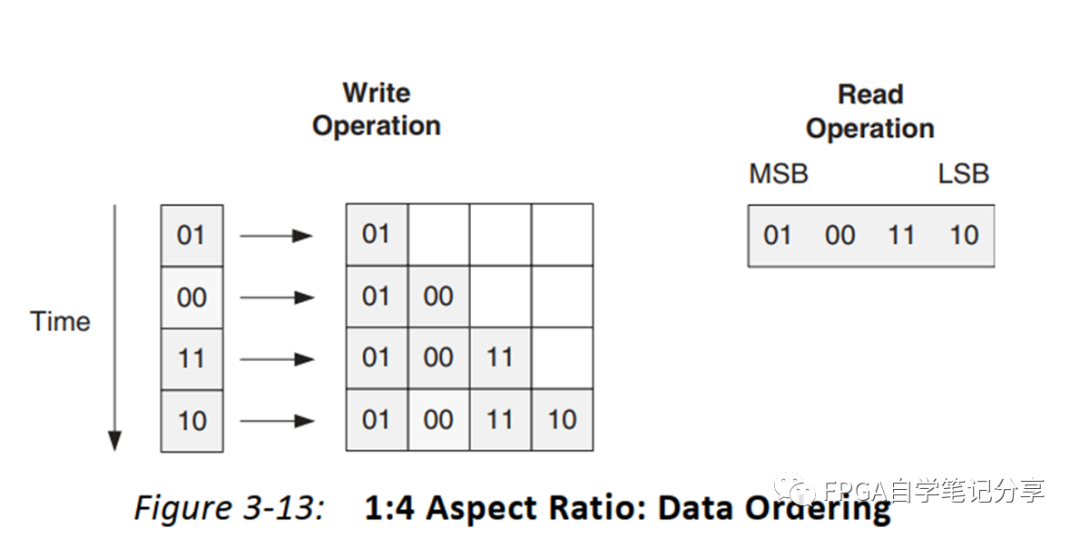

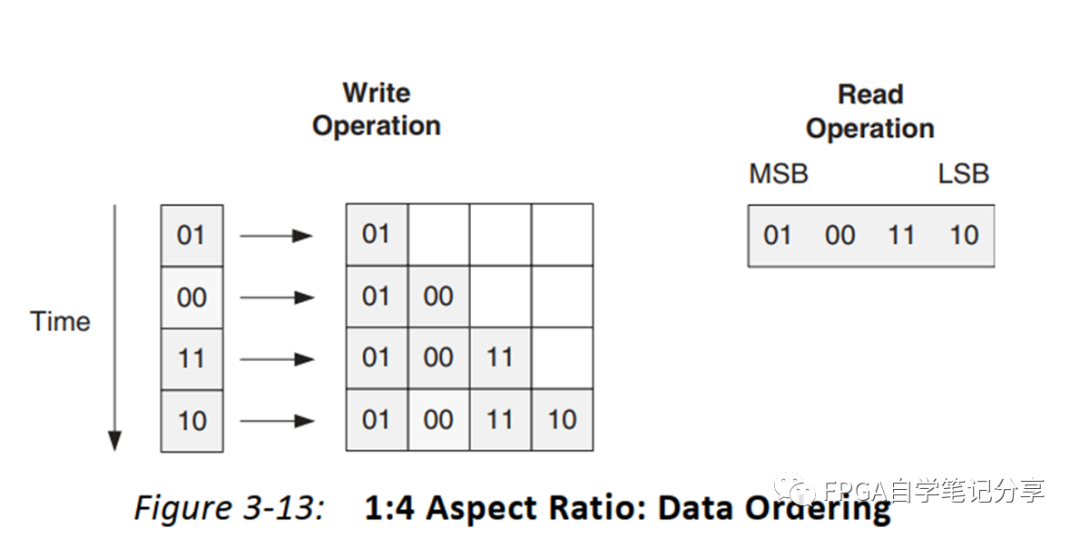

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 759

759

电子发烧友网站提供《采用FPGA实现医疗成像总结.pdf》资料免费下载

2023-10-07 16:34:21 2

2

电子发烧友App

电子发烧友App

评论