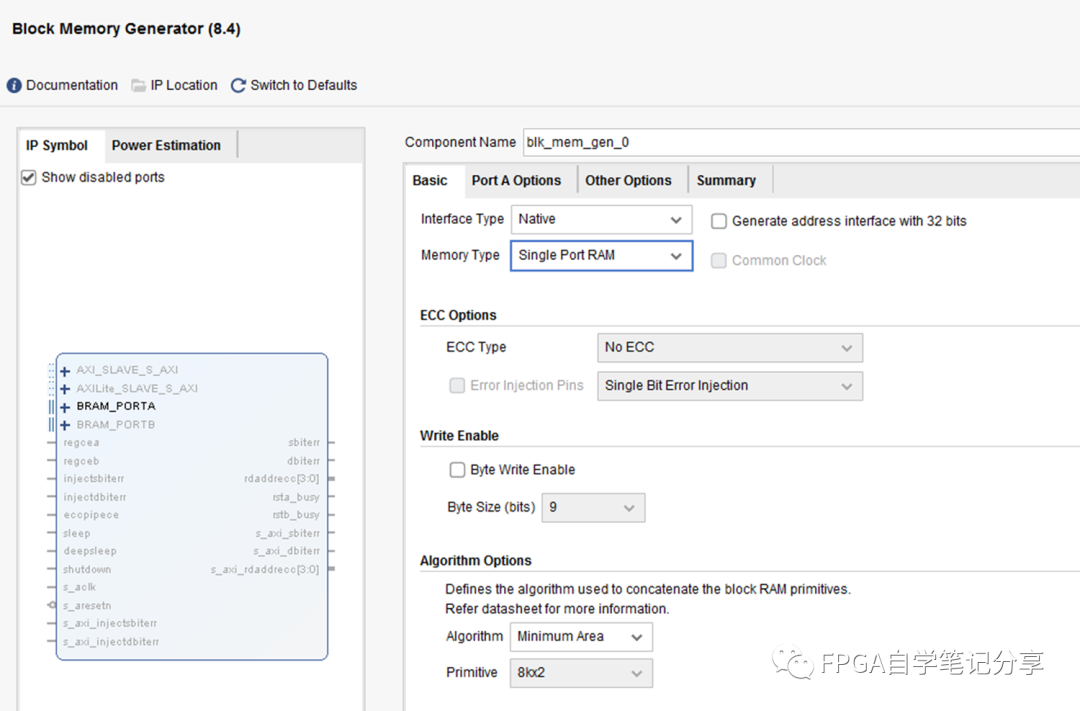

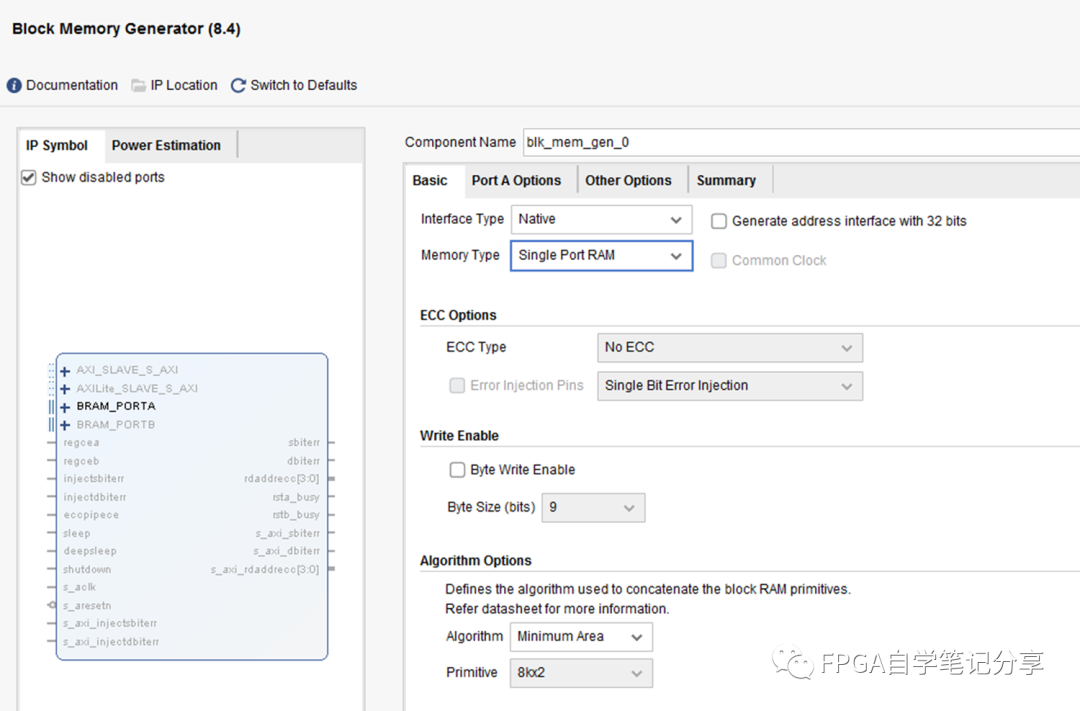

Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

2023-11-14 17:49:43 736

736

你好: 我是一个购买的帐户,所以我的许可证应该允许访问所有内容。但是当我使用System Generator for DSP时,系统说我的SysGen签出许可证失败了。有人知道怎么解决吗?谢谢

2019-01-28 07:16:36

错误:System Generator for DSP(SysGen)的许可证签出失败。无法联系Xilinx许可证管理器。请检查以下内容:(1)XILINX环境变量指向有效的ISE安装(2

2018-12-29 10:35:12

FPGA中的数字控制器是什么?System Generator中的PID控制器是如何设计的?

2021-04-08 06:51:46

大家好,这是我第一次使用System Generator工具,如果有人能够解决一个不让我继续参与我的硬件协同仿真项目的问题,我想。我正在使用Matlab R2013b,Xilinx ISE 14.7

2020-03-23 06:53:11

根据我的理解,System Generator是MatLab到RTL的转换,因此不包括Vivado的优化过程。问题1--是真的。确实,Vivado中的优化将大大改变系统描述,而系统描述不会向后兼容

2019-04-25 12:47:45

XILINX Core Generator的官方教学PPT

2012-08-15 18:44:59

design example.Just wondering Xilinx has any application notes and system generator design examples? Thanks,Will

2019-01-30 10:08:42

HI,我正在使用System Generator 2014.4 30天评估包,Matalb 2014B。简单地说我想使用FIR编译器,当我尝试编辑它的参数时,我得到了两个错误: - 1.“来自MEX

2020-03-24 09:01:59

with FIR compiler 5.0 , in system generator. When i givea inputsinewave( amplitude of 1, 1 MHz

2019-02-12 11:20:48

嗨,我在系统生成器2014中使用黑盒子.4在模拟模式下选择vivado模拟器。如果我运行该项目它正常工作,但如果我在系统生成器或黑盒vhdl中更改某些内容,则会出现此错误:Xilinx模块库中发

2018-10-30 11:07:57

你好!我试图通过系统生成器生成FFT的组件。我浏览了.mdl文件中的Stystem Generator块,但是当我尝试生成时,我收到以下错误消息。我不明白为什么它无法连接到许可证管理器。我已经通过

2018-11-27 14:22:40

, I have this basic doubt that why at all HDL coder is there in Matlab when we have system generator

2018-12-18 10:40:58

/fpga-design/simulink-with-xilinx-system-generator-for-dsp.htmlhttp://www.mathworks.cn/searchresults/?c%5B%5D

2013-10-05 11:59:34

USE和System Generator何时才能胜任64位Windows 7?以上来自于谷歌翻译以下为原文When will ISE and System Generator be qualified for 64 bit Windows 7?

2018-11-26 15:05:56

最近在搞system generator仿真,发现getway in这个模块参数设置变化导致MATLAB闪退问题,贴图如下其中getway in 这个模块数据类型换成定点有符号或者无符号数都不得行,换成布尔值又会出现错误,不知为何啊!求教。

2018-01-05 21:43:53

翻译成verilog,在FPGA里面实现,即system generator。altera有没有类似的接口,与matlab可以互连,直接在matlab里设计我所需要的算法,在翻译成verilog?

2015-01-14 14:20:50

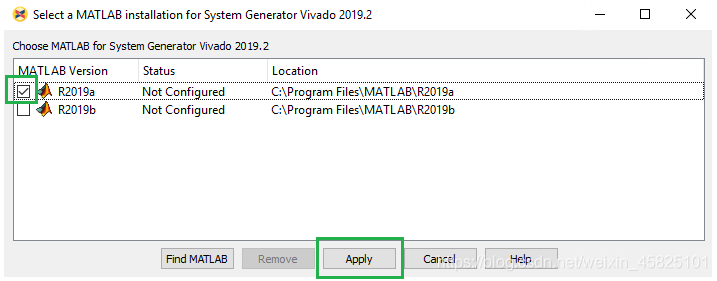

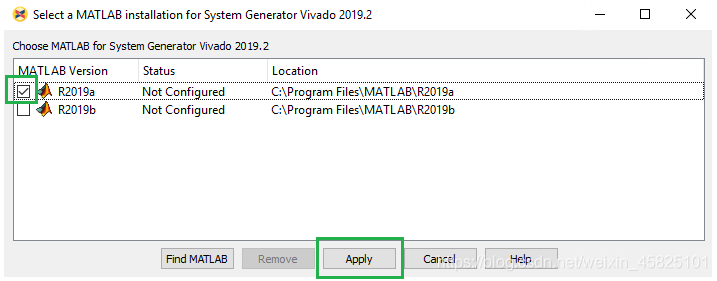

. But when it comes on selecting Matlab version for System generator 10.1 it displays both versions

2019-05-27 06:30:15

我的工程应用中需用Xilinx10.1中的fifo核,具体步骤如下:1、在CORE generator下建立My232coregen.cgp文件,选择以下功能: 图1.2、进入fifo

2012-05-15 19:02:08

我用system generator打开matlab,simulink库列表中跟多xilinx的库什么模块也没有,还出来这个窗口,请问怎样把对应的模块显示出来,或从哪里找?谢谢

2018-01-19 10:37:50

组的FPGA实现7.7 本章小结第8章基于System Generator的DSP系统开发技术8.1 System Generator的简介与安装8.1.1 System Generator简介

2012-04-24 09:23:33

,使用System Generator有三大优势:第一,图形化操作,简单易用;第二,实现的算法能确保与仿真结果相符;第三,无需为仿真和实现建立不同的模型。因此,利用 System Generator可以大幅度减少用FPGA设计DSP的工作量,缩短开发周期。

2019-06-21 06:25:23

各位好,最近在使用system generator 搭建一个ifft设计模块,使用ise调用,但是在下载到板子后,示波器输出波形去在没有输入的情况下仍然有波形,确定不是噪声,波形还是很规律,求解释呀!

2016-07-13 13:21:30

使用system generator导入xilinx模块时,只要连线两个模块,matlab就崩溃,有知道原因的大佬吗?

2018-01-19 17:54:57

Xilinx system generator on Matlab with Vivado With ISE there is an application call System Generator

2018-12-27 10:57:02

Suite下。在我的PC上,Xilinx System Generator嵌套在Vivado下。可以使用基于Vivado的System Generator来开发ISE系统吗?或者是否有必须安装

2018-12-27 10:55:34

大家好,我正在使用具有Virtex-4 FX100的定制板。在内部,有一个基于VHDL的框架,它将定制板上的不同部分与“DSP内核”连接,后者是在System Generator下开发的。在这

2019-01-15 10:39:11

在system generator中,我把(-128~127),变为(-1~1),但是下载到硬件中,使用chipscope抓取到的数据确实(-128~127),请问是怎么回事

2016-08-10 15:32:38

有做System Generator处理图像的吗?遇到一些问题,一起商量下

2020-09-28 19:04:58

嗨,我正在尝试学习如何使用System Generator来创建自己的IP核。首先,我在DocNav中找到了一个ug948-vivado-sysgen-tutorial文档。我在哪里可以找到本文档中描述的示例?我在安装目录中的“examples”文件夹中找不到完全相同的示例。提前致谢马丁

2020-05-22 07:22:09

this system generator?Is this a part of xilinx ISE design tool.If so please give me idea how can I use it to generate the sinc signals?thank you

2019-01-28 06:37:12

您好,我被要求执行序列生成器。我已经用纸做过一切,但我不知道如何在Xilinx上正确创建它。我完成了转换表和输出表。我的输出函数已经用karnaugh等进行了简化。但是当我实现它时,我认为它在

2019-01-10 10:39:50

各位大佬,我在安装System Generator时,跟着教程走,发现在vivado中没有出现System Generator for DSP这个选项,请问是我哪里安装得不对吗?

2023-09-26 21:54:58

当我完成SDx 2017.2的安装时,没有安装System Generator的选项。我正在运行从Xilinx下载的安装程序:https://www.xilinx.com/member/forms

2019-01-07 10:59:00

你好,我叫Joaquín。有人知道,我可以在Matlab / Simulink中使用System Generator创建一个双向(inout)端口。我正在尝试为Xilinx的外部存储器创建一个接口

2019-05-09 14:36:24

...以上来自于谷歌翻译以下为原文Hi all!!! I am implementing ofdm using xilinx system generator.In the transmitter

2019-04-19 10:32:12

最近在使用system generator设计一个rs编码译码的模型,总的思想是在rs编码产生信号后,插入一个误码,然后作为信号源进行解码,看是否能够正常的进行解码,求解是怎么才能把rs编码后的信号存储起来作为信号源

2016-07-20 20:13:59

嗨,我刚刚安装了ISE 14.7系统版本,并将System Generator链接到MATLAB(2014a)。但是当我尝试打开simulink以使用Xilinx System Generator

2018-12-12 10:54:08

2014.3.1) itself ? Couldn't find the RESOURCE ESTIMATOR block inthe system generator [xilinx

2019-04-02 14:32:18

有用Xilinx的system generator做图像处理的嘛?求交流 。我正在用这个做图像处理,已经用了3个月了,在做一些算法,遇到一些困难,求一起交流学习。发现用这个开发的人真不多啊。

2014-05-09 14:57:21

非常苦恼,刚开始学习system generator,用带光盘的书上的例子,想要学习一下设计流程,结果屡屡碰壁。在搭建好系统,点击开始仿真之后,总是会出错。在别人的电脑上就能仿真成功,一开始认为是

2016-07-13 23:12:36

xilinx公司的网络教程“利用 System Generator 进行 DSP 设计”谁有?上传一份给小弟吧

2013-03-14 12:17:03

解决方案以上来自于谷歌翻译以下为原文hi,i have used xilinx 14.1 and matlab2012awhen i opened a system generator it shows

2019-03-11 14:17:09

System Generator。我已使用下载站点上提供的WebPACK_82i_SFD.exe重新安装了ISE 8.2i。但是,系统生成器仍然不可用。我需要做什么才能将系统生成器“重新安装”到Matlab中

2018-11-19 14:42:56

简化Xilinx和Altera FPGA调试过程:通过FPGAViewTM 解决方案,如混合信号示波器(MSO)和逻辑分析仪,您可以在Xilinx 和Altera FPGA 内部迅速移动探点,而无需重新编译设计方案。能够把内部FPGA

2009-11-20 17:46:26 26

26

采用Gardner算法,对QPSK调制解调系统中的位同步系统进行设计与实现,大大提高了系统性能和资源利用率。重点阐述采用FPGA开发环境System Generator系统设计工具进行位同

2010-07-21 16:12:40 26

26 深入了解赛灵思System Generator中的时间参数

基于模型的设计(MBD)因其在缩小实时系统抽象的数学建模和物理实现之间差距方面的光明前景而备受关注。通过使用相同的

2009-12-29 11:40:30 1300

1300

HDL设计和验证与System Generator相结合

Xilinx®SystemGeneratoRForDSP是用来协助系统设计的MATLABSimulink模块集。SystemGeneratorforDSP在熟悉的MATLAB环境中引入XilinxFPGA对象,让您能够

2010-01-06 14:39:30 1181

1181

基于软件无线电的思想,阐述了第四代移动通信核心技术OFDM的原理及其IFFT/FFT实现的数学模型,并且提出了OFDM调制的核心部分IFFT的软件实现方法,即采用XILINX公司的System Generator这一高

2011-05-05 17:02:59 91

91 该设计是基于System Generator设计平台,在Matlab/Simulink环境下搭建系统模型,再进行功能仿真和验证,完成QPSK调制器的设计。仿真结果表明,所设计的调制器能产生正确QPSK波形,达到了预期效果

2011-10-17 16:10:51 65

65 Xilinx公司推出的DSP设计开发工具System Generator是在Matlab环境中进行建模,是DSP高层系统设计与Xilinx FPGA之间实现的桥梁。在分析了FPGA传统级设计方法的基础上,提出了基于System Generator的

2013-01-10 16:51:24 58

58 Xilinx FPGA工程例子源码:System Generator的设计实例

2016-06-07 14:41:57 22

22 、乘加(MACC, ),乘加,三输入加法等等。该架构还支持串联多个DSP48E1 slice,避免使用fpga逻辑功能的繁琐。 System generator DSP48E1 模块参数 双击dsp48e1模块

2017-02-08 01:07:12 595

595

环境 Matlab 2014 a Vivado 2014.4 System generator 2014.4 实现步骤 1、模型搭建与仿真 在simulink环境下工程搭建如下 图3 四路加

2017-02-08 01:10:08 473

473

赛灵思(Xilinx)近期宣布推出高阶设计工具2015.3版DSP系统产生器(System Generator),可让系统工程师运用Xilinx All Programmable组件设计高效能DSP系统。

2019-10-06 18:00:00 283

283 最新版 DSP 系统生成器 ( System Generator for DSP ),是设计高性能 DSP 系统的业界领先高级工具,不仅可实现较高层次的设计抽象性,而且还可可通过整合

2017-02-08 20:41:18 254

254 一直都在System Generator下做图像处理相关的算法,感觉SysGen挺强大的,前几天突发奇想,能否直接用SysGen实现数据的通信呢,毕竟一句HDL代码都不写对于做FPGA的人来说却是很有吸引力的。

2017-02-10 19:51:11 2618

2618

前一阵一直在忙,所以没有来得及写博文。弄完杂七杂八的事情,又继续FPGA的研究。使用Verilog HDL语言和原理图输入来完成FPGA设计的方法都试验过了,更高级的还有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10:11 8192

8192

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可是设置

2017-02-11 11:53:11 3778

3778

system generator是xilinx公司的系统级建模工具,它是扩展mathworks公司的MATLAB下面的simulink平台,添加了XILINX FPGA专用的一些模块。加速简化了FPGA的DSP系统级硬件设计。

2017-02-11 19:21:33 7386

7386

利用System Generator软件平台,实现基于模块化建模方法的变换器建模,并简化语言编写控制系统的复杂过程。研究了从MATLAB-Xilinx环境中导出使用模块化建模方法搭建的控制算法。通过

2017-11-15 14:31:34 4985

4985

的对应关系: System generator 安装之后会在Simulin模块库中添加一些Xilinx FPGA专用的模块库,包括Basic Element,Communication,Control

2017-11-17 14:29:06 7298

7298 在FPGA平台上应用System Generator工具实现了高精度频率估计Rife算法。不同于传统的基于HDL代码和IP核的设计方法,采用System Generator工具可以使复杂算法

2017-11-18 09:01:51 2208

2208

Xilinx System Generator 是专门为数字信号算法处理而推出的模型化设计平台,可以快速、简单地将DSP系统的抽象算法转换成可综合的、可靠的硬件系统,弥补了大部分对C语言以及Matlab工具很熟悉的DSP工程师对于硬件描述语言VHDL和Verilog HDL认识不足的缺陷。

2018-07-19 09:32:00 3716

3716

PLD/FPGA 常用开发软件System Generator 9.10。 业内领先的高级系统级FPGA开发高度并行系统。

2017-11-26 11:34:56 12

12 本视频产品演示介绍了 Xilinx 系统生成器(System Generator)和 Xilinx ISE® 项目浏览器(Project Navigator)设计环境之间的新整合。

2018-06-06 13:46:00 3024

3024

新的System Generator,算法开发人员可在其熟悉的MATLAB和Simulink模型化设计环境中创建生产质量级的DSP实现方案,而且相校传统 RTL 可大幅缩短设计时间。最新版提供了更高级的设计抽象,并可通过新型的模块集中、更快的仿真和编译运行时间,将无线电算法的设计生产力提高7倍。

2018-08-20 10:13:00 763

763 了解如何将Vivado HLS设计作为IP模块整合到System Generator for DSP中。

了解如何将Vivado HLS设计保存为IP模块,并了解如何将此IP轻松整合到System Generator for DSP的设计中。

2018-11-20 05:55:00 2940

2940 了解如何在System Generator中使用多个时钟域,从而可以实现复杂的DSP系统。

2018-11-27 06:42:00 3450

3450 了解如何使用Vivado System Generator for DSP进行点对点以太网硬件协同仿真。

System Generator提供硬件协同仿真,可以将FPGA中运行的设计直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

4262 System Generator 数字上下变频 (DUC/DDC)模块集的易用性大幅提升,使得更加便于无线算法开发。这些新型模块还添加了有助于加速验证和编译运行时间的增强功能,所有这些模块提供了七八种参数设置。

2019-07-31 09:22:49 2293

2293 根据椭圆曲线密码体制的几种关键算法,采用Modelsim仿真工具设计相应的算法模块。然后将各模块代码通过System Gene

2021-06-12 10:17:00 1294

1294

本篇博文是面向希望学习 Xilinx System Generator for DSP 入门知识的新手的系列博文第一讲。其中提供了有关执行下列操作的分步操作方法指南。

2022-02-16 16:21:36 1578

1578

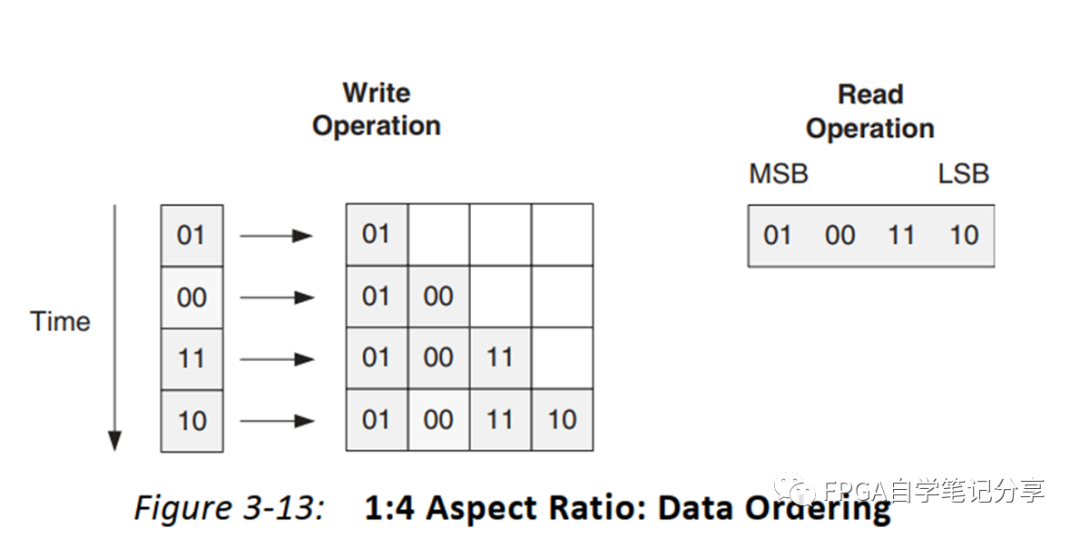

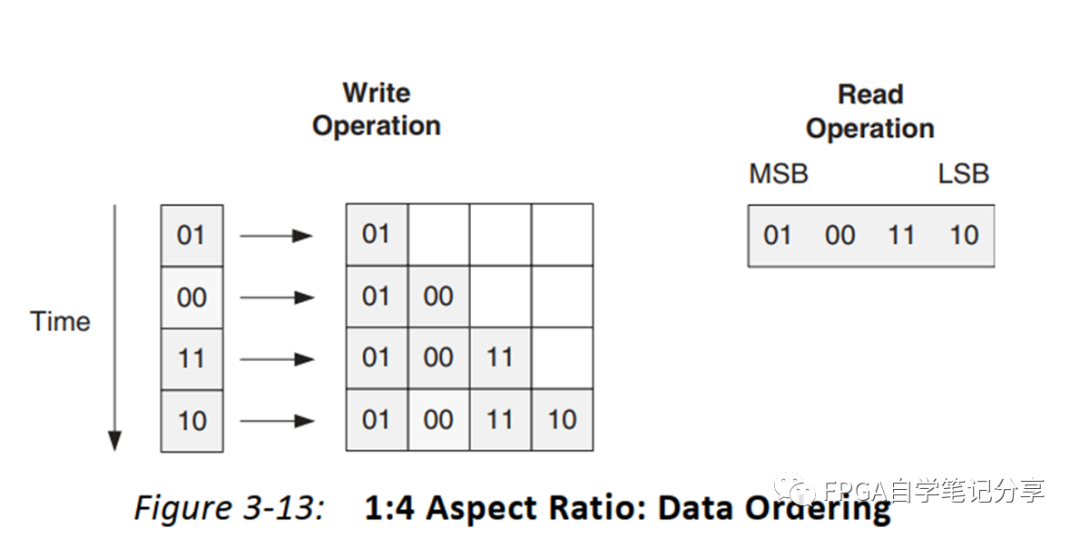

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 759

759

电子发烧友App

电子发烧友App

评论